250220-007_第9个项目_TD4CPU复刻

(2025-02-20 10:40:13此文档已被发布到数字花园博客网站中)

基于https://github.com/Eraser2333/TD4CPU项目,复刻而来。

做这个玩具的初衷是最近学Linux有一段时间学不下去了感觉太难了,为了换换心情,所以买了本自制CPU的书,看完之后对FPGA比较感兴趣,所以为了深入了解CPU的内部结构和原理,就动手复刻了一款比较简易的CPU。

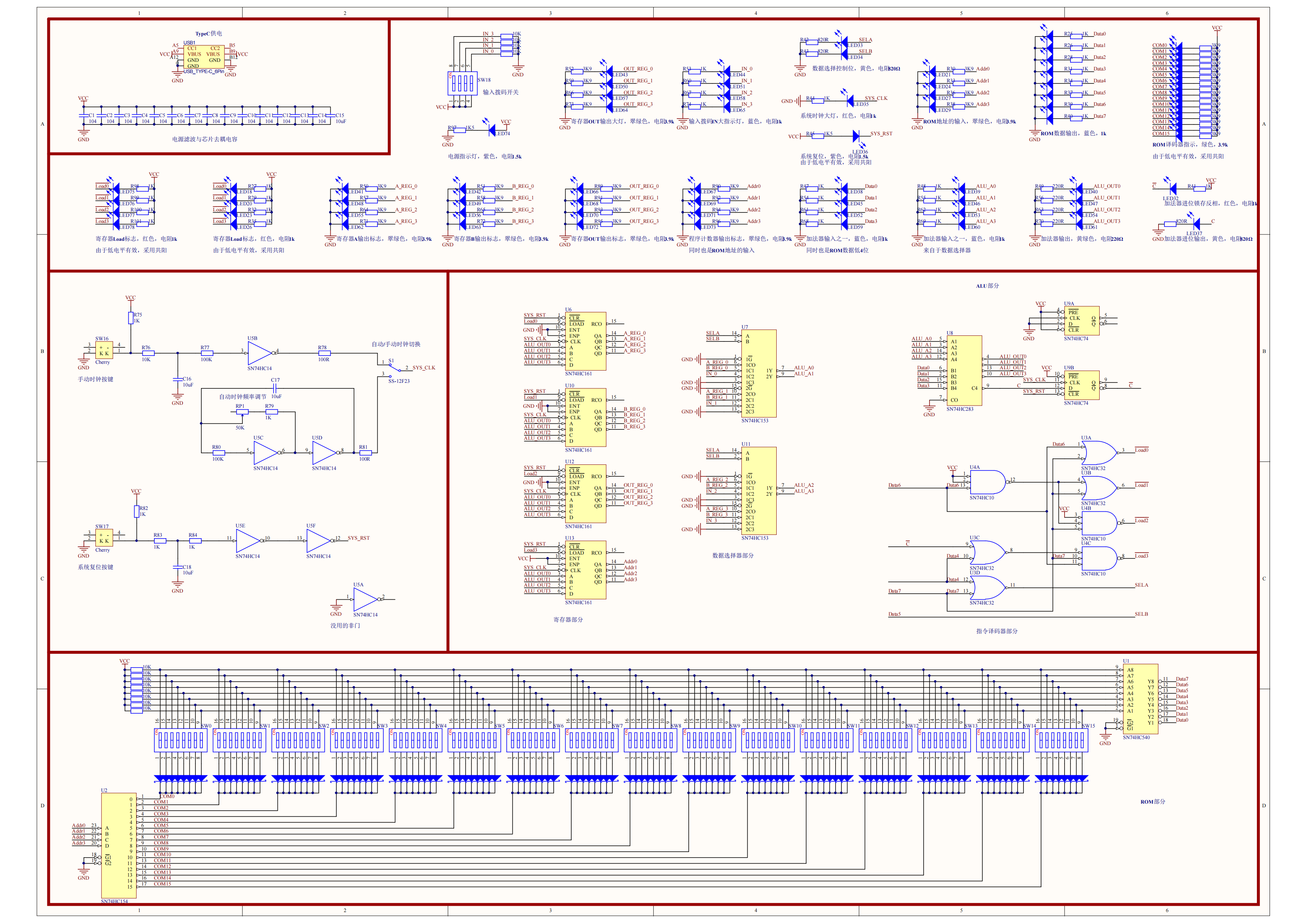

硬件电路原理图:

TD4CPU是一款基于TTL逻辑门构建的极简4位教学用CPU,其硬件架构和电路原理图体现了早期计算机设计的核心逻辑。

其核心架构可分为以下模块:

时钟模块 采用RC振荡电路生成主时钟信号,支持两种运行模式:连续运行(约1Hz-10kHz)和单步调试。 时钟信号通过74LS14双D触发器分频后驱动程序计数器(PC)和指令执行周期。

程序计数器(PC) 由4位同步计数器74LS161实现,最大寻址16字节ROM空间。 支持跳转指令(JMP/JNC)时通过74LS283加法器计算目标地址,并利用74LS157多路复用器切换PC输入源。

ROM存储单元 使用16组DIP拨码开关手动编程,每组对应4位操作码(Opcode)4位立即数。 指令读取通过74LS154 4-16译码器选择当前PC指向的ROM位置,数据总线直接连接至寄存器组。

寄存器与ALU A/B寄存器:采用74LS161 4位锁存器,支持数据加载和输出使能控制。 ALU运算单元:核心为74LS283 4位全加器,通过译码电路选择操作行为。执行加法运算时自动更新进位标志(C Flag),由74LS74存储进位状态。 输入/输出端口:通过74LS153数据选择器连接外部ROM,支持4位并行数据传输。

控制逻辑 指令解码器由74LS32和74HC10与非门构成,将4位操作码转换为寄存器加载、ALU使能等控制信号。 典型指令周期包括:取指→解码→执行→PC更新,耗时2-4个时钟周期。

信号路径:

时钟信号 → PC计数器 → ROM地址选择 → 指令读取 → 控制信号生成

↓

寄存器/ALU数据流:A/B寄存器 ↔ 加法器 ↔ 进位标志 ↔ 输出端口

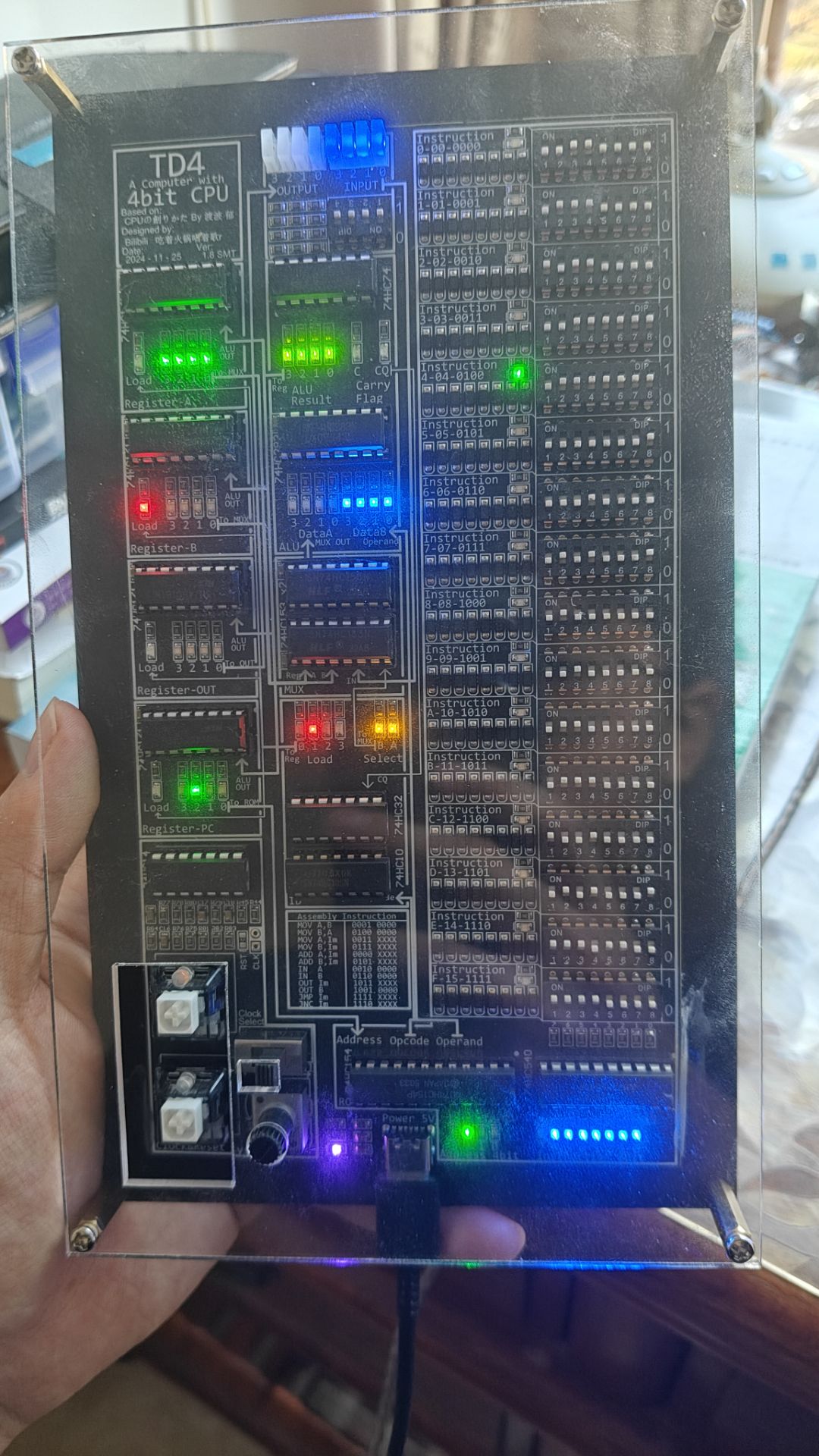

ps:复刻的时候没有仔细看文档,结果焊完电路板找不到安装孔,直接用热熔胶粘上亚克力板去的哈哈(

上电成功正常运行,逻辑完备、现代CPU程序执行三大特征:顺序执行、条件执行和循环(跳转)执行均已实现。

汇编语言测试程序:

00110000 MOV A,0000

01110000 MOV B,0000

10110000 OUT 0000

00111111 MOV A,1111

01111111 MOV B,1111

00000001 ADD A,0001

00010000 MOV A,B

01010001 ADD B,0001

01000000 MOV B,A

00100000 IN A

01100000 IN B

01110000 MOV B,0000

10010000 OUT B

01010001 ADD B,0001

11101100 JNC 1100

11110000 JMP 0000